최첨단 반도체용 회로선 폭 10nm의 나노임프린트용 템플릿 개발

1.4nm 세대 상당의 반도체에 대응하는 회로선폭의 미세화와 제조 비용 절감의 요구에 대응

2025년 12월 9일

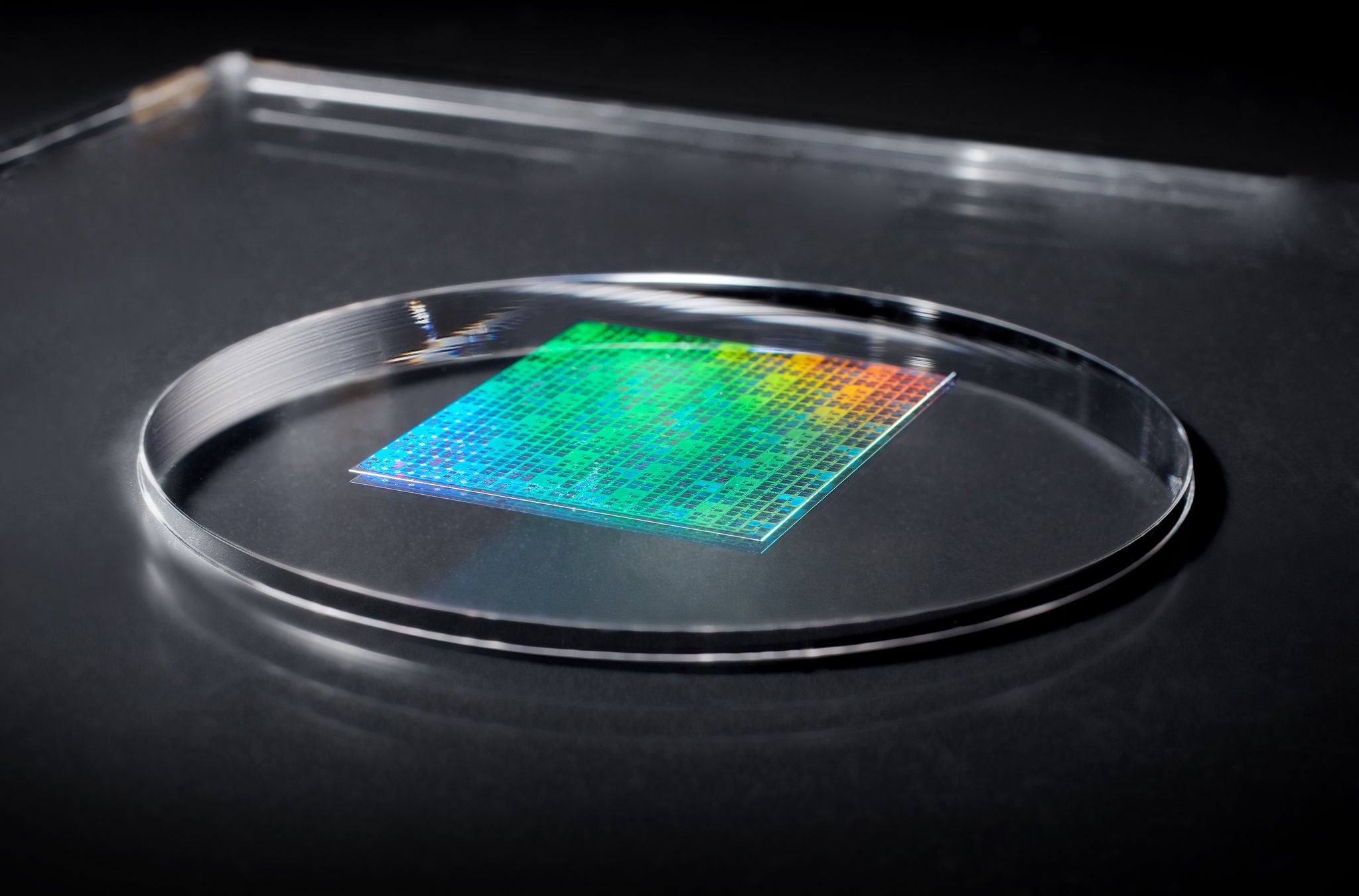

다이 니혼 인쇄 주식회사 (본사 : 도쿄 대표 이사 사장 : 기타시마 요시이 이하 : DNP)는 반도체의 회로 패턴 형성에 사용하는 나노 임프린트 리소그래피 (Nano-Imprint) Lithography:NIL)※1용으로, 1.4나노미터(1nm=10억분의 1미터) 세대 상당의 로직 반도체에도 대응 가능한, 회로선폭 10nm의 템플릿(형)을 개발했습니다. 이번에 개발한 선폭 10nm의 NIL용 템플릿은 NAND형 플래시 메모리에 더해 스마트폰이나 데이터 센터 등에서 사용되는 최첨단 로직 반도체의 미세화 요구에 부응합니다.

NIL용 템플릿 개발의 목적과 경위

최근, 다양한 기기의 고성능화에 따라, 첨단 반도체에서는 한층 더 미세화가 요구되고 있어 EUV(Extreme Ultra-Violet: 극단 자외선) 리소그래피에 의한 생산이 진행되고 있습니다. 한편, 생산 라인의 구축이나 노광 공정에 비교적 많은 비용이나 전력이 필요하기 때문에, 제조 비용 삭감과 환경 부하 저감의 양립이 급무가 되고 있었습니다. DNP는 2003년부터 회로 패턴을 새긴 템플릿을 기판에 직접 압착하여 전사함으로써 노광 공정의 전력 소비량을 억제할 수 있는 NIL용 템플릿을 개발하여 독자적인 노하우를 축적해 왔습니다.

이번에 EUV 리소그래피의 일부 공정의 대체나 EUV 리소그래피의 생산 프로세스를 갖지 않는 고객의 요구에 대응해, 첨단 영역의 로직 반도체의 제조를 가능하게 하는 회로선폭 10nm의 NIL용 템플릿을 개발했습니다. DNP는 이 템플릿의 공급을 통해 고객의 반도체 제조 공정의 선택을 확대하고, 제조 비용 절감과 환경 부하 저감의 양립에 연결해 나갈 것입니다.

새롭게 개발한 회로선폭 10nm의 NIL 템플릿의 특징

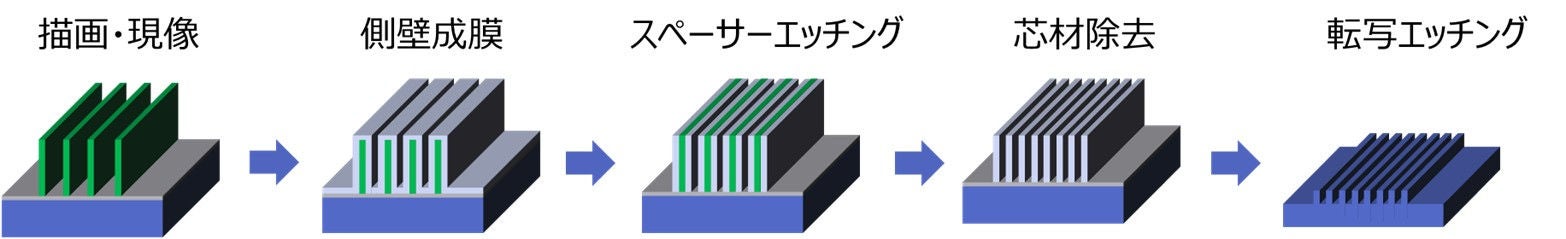

○ 묘화 장치에 의해 형성한 패턴에 성막·에칭을 실시해 패턴의 밀도를 2배로 하는 더블 패터닝(Self-Aligned Double Patterning:SADP)을 활용해, NIL 템플릿의 미세화를 실현했습니다.

○DNP가 길러 온 포토마스크 제조의 기술・노하우에 더해, 웨이퍼의 제조 프로세스의 기술도 응용해, 회로선폭 10nm의 NIL 템플릿을 개발했습니다.

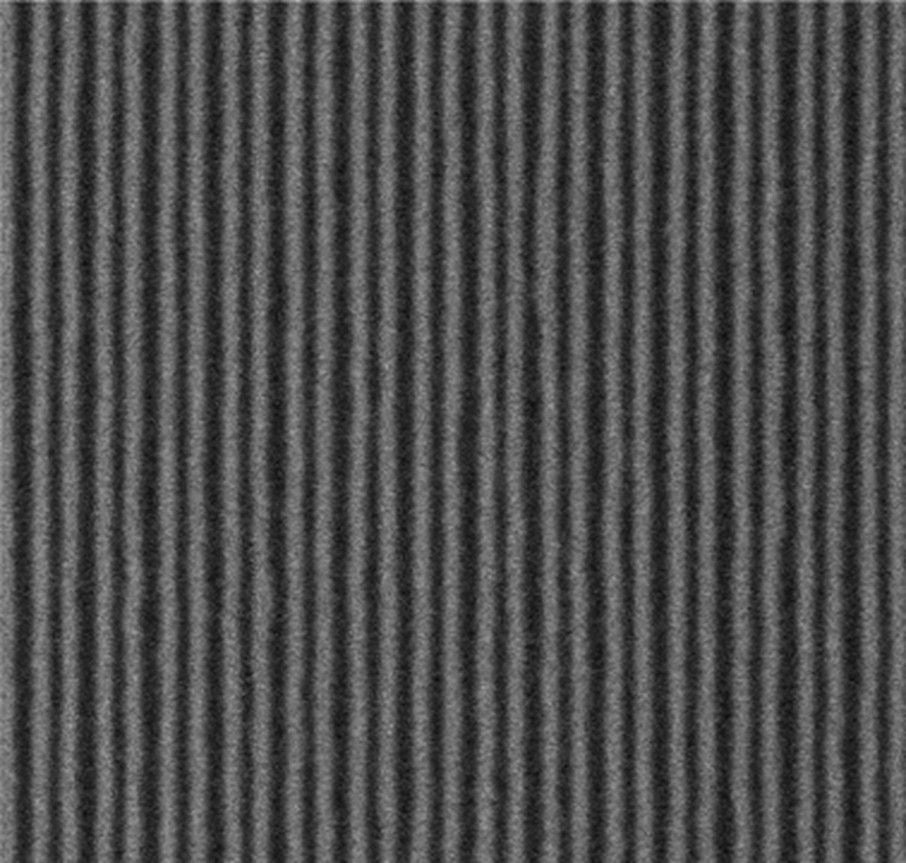

나노 임프린트의 포토 마스크상의 선폭 10nm의 Line & Space 패턴 이미지

나노 임프린트의 포토 마스크상의 선폭 10nm의 Line & Space 패턴 이미지

○향후 추가 확대가 예상되는 첨단 로직 반도체의 회로선폭의 미세화 요구에 대응합니다.

○첨단 반도체 제조의 노광 공정에서의 전력 소비량을 삭감합니다. 「NIL에 의한 초미세 반도체의 에너지 절약 가공 기술」에 의해, 종래의 ArF(불화 아르곤) 액침이나 EUV 등의 노광 공정과 비교해, 전력 소비량을 약 10분의 1로 억제할 수 있습니다. ※2

미래 전개

DNP는 반도체 메이커 등의 고객과의 대화를 깊게 해, 반도체의 미세화 요구 등을 선취해, NIL용 템플릿의 평가 워크를 개시하고 있어, 2027년에 양산 개시를 목표로 합니다. 이어 반도체의 추가 미세화와 비용 절감을 위해 NIL용 템플릿의 한층 더 개발과 수요 확대에 대응한 생산 체제의 강화를 진행시켜 2030년도에 NIL에서 40억엔의 매출 증가를 목표로 합니다.

덧붙여 2025년 12월 17일~19일에 도쿄 빅 사이트(국제 전시장)에서 개최되는 「SEMICON Japan 2025」의 DNP 부스(동 6홀·부스 번호:E5936)에서 본 제품을 전시합니다.

- 1 나노임프린트 리소그래피: 기재상의 수지 등에 금형 템플릿을 압착하여 nm(나노미터: 10-9미터)~μm(마이크로미터: 10-6미터) 단위의 선폭의 회로 패턴을 안정적이고 저렴하게 전사하는 미세 가공 기술.

- 2 NILによる超微細半導体の省エネルギー加工技術 → https://www.dnp.co.jp/news/detail/10162455_1587.html

- 기재되어 있는 회사명・상품명은, 각사의 상표 또는 등록 상표입니다.

- 기재 내용은 발표일 현재의 것입니다. 향후 예고 없이 변경될 수 있으니 미리 양해 바랍니다.