DNP Achieves 10nm Line-pattern resolution on Nanoimprint Template for Cutting-Edge Semiconductors

Supports 1.4nm Generation Semiconductors, Reduces Manufacturing Costs and Energy Consumption

Dec 9, 2025

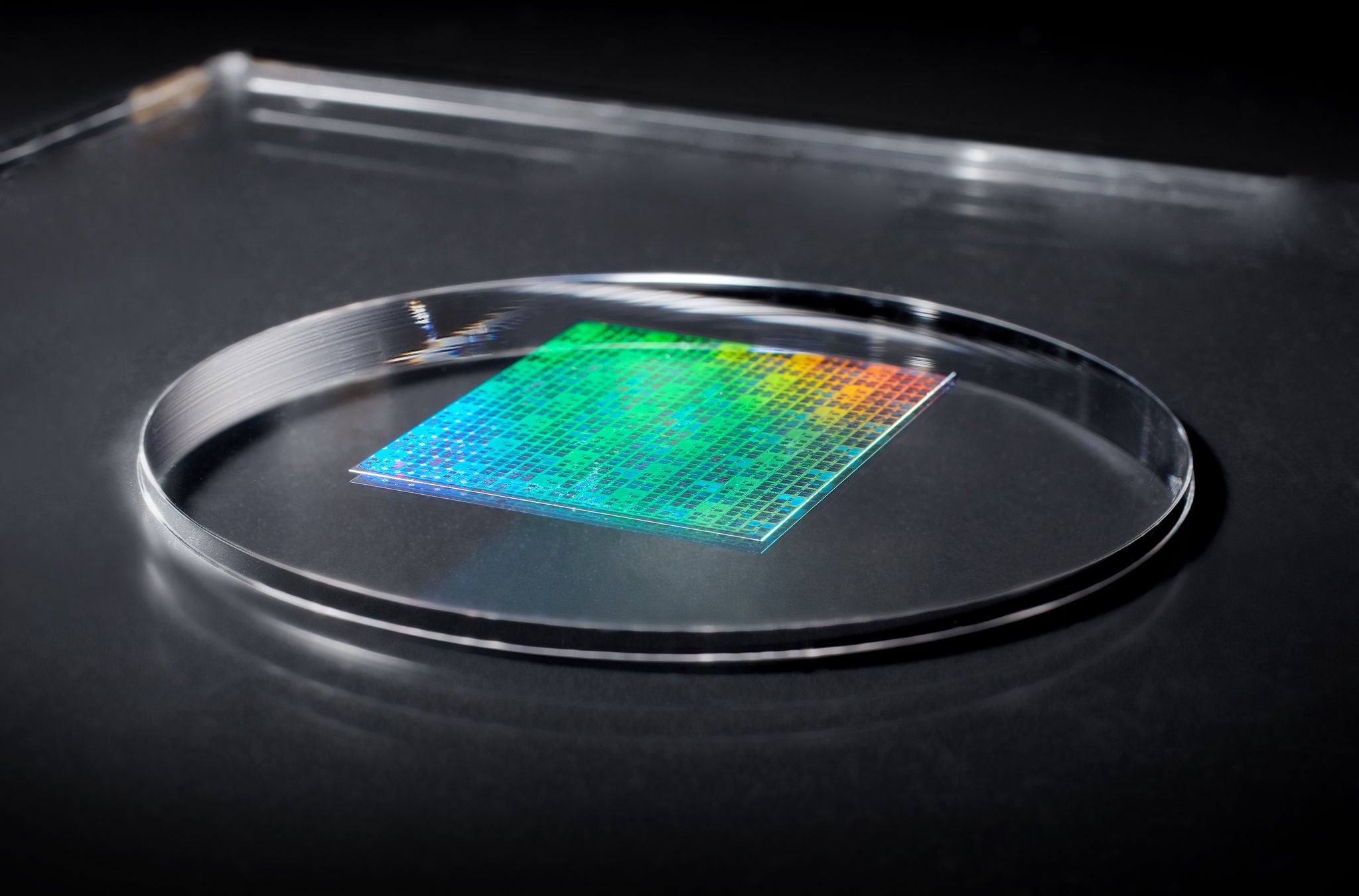

December 9, 2025 Tokyo, Dai Nippon Printing Co., Ltd. (DNP) today announced the development of a nanoimprint lithography (NIL) template1 featuring a circuit line width of 10 nanometers (nm: 10-9 meter). The new template enables patterning for logic semiconductors equivalent to the 1.4nm generation and meets the miniaturization needs of cutting-edge logic semiconductors used in devices such as smartphones, data centers, and NAND flash memory.

Background and Aims

In line with the shift to more sophisticated devices seen in recent years, demands have emerged for even greater miniaturization in cutting-edge semiconductors, leading to advances in Extreme Ultra-Violet (EUV) lithography-based production. EUV lithography, however, requires substantial capital investment, energy consumption, and operating costs in building production lines and the exposure process. This has fed into the pressing need to balance a reduction in manufacturing costs with a lowering in the environmental burden. Since 2003, DNP has been developing NIL templates, used to press circuit patterns directly into substrate materials, allowing manufacturers to reduce energy consumption in the exposure process. Over the following two decades, DNP has successfully accumulated extensive know-how in high-precision patterning.

In this latest development, DNP has developed a NIL template with a 10nm line pattern. It can replace a portion of the EUV lithography process, facilitating the manufacture of cutting-edge logic semiconductors for clients that do not have EUV lithography production processing. By supplying the new template, DNP will expand the options available to clients involving semiconductor manufacturing processes, helping to reduce both manufacturing costs and the environmental burden.

Key Features

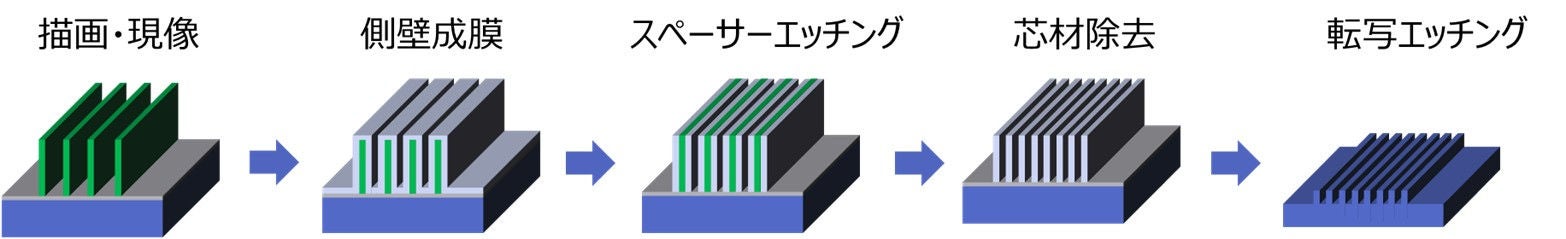

DNP has successfully achieved further miniaturization of NIL templates by leveraging Self-Aligned Double Patterning (SADP), which doubles pattern density through film deposition and etching a pattern formed by an electron beam mask writer.

In addition to the photomask manufacturing technology and know-how cultivated by DNP, wafer manufacturing process technology has also been applied to develop the new NIL template with a circuit line width of 10nm.

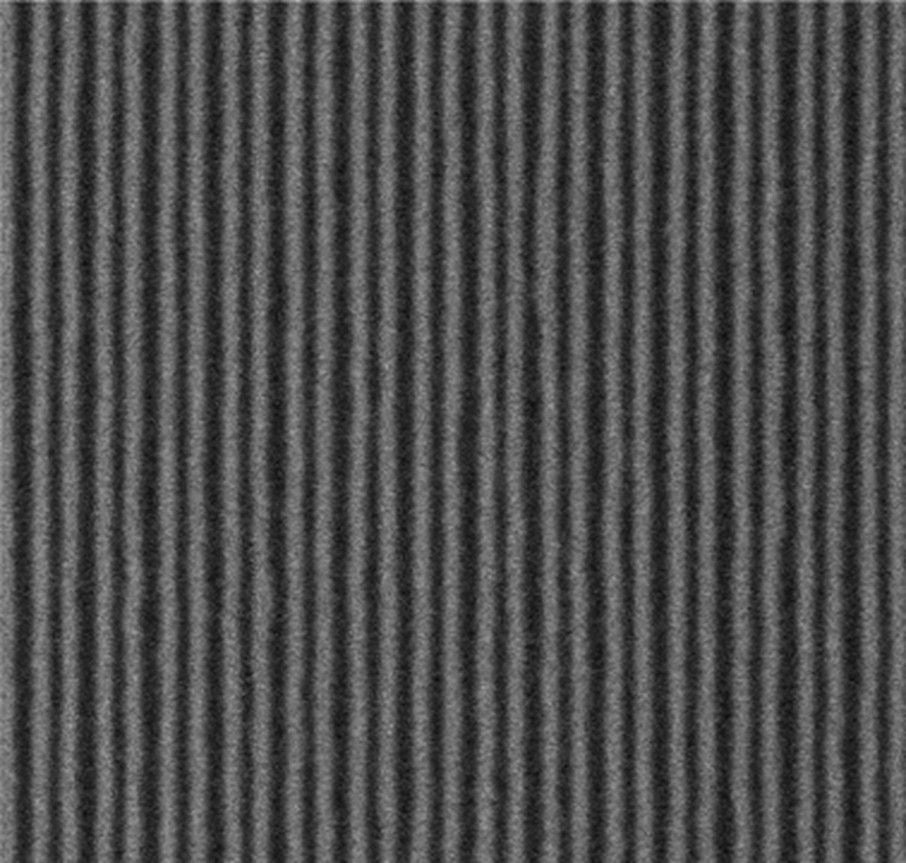

Line & Space pattern image with 10nm line width on the new nanoimprint template

Line & Space pattern image with 10nm line width on the new nanoimprint template

The new NIL template answers the need for finer circuit line widths in advanced logic semiconductors, which are expected to continue expanding in the future.

The technology also reduces power consumption in the exposure process of cutting-edge semiconductor manufacturing. Driven by an energy-saving processing technology for ultra-fine semiconductors using NIL, it is now possible to reduce power consumption to approximately one-tenth of currently available exposure processes, such as Argon Fluoride (ArF) immersion and EUV2.

Going Forward

Anticipating semiconductor miniaturization needs, DNP is engaging in a deeper dialogue with semiconductor manufacturer clients. We have begun evaluation work for NIL templates, and aim to start mass production in 2027. DNP will advance the further development of NIL templates and enhance production capacity to meet growing demand, targeting increased NIL sales of 4 billion yen in FY 2030.

The new 10nm NIL template will be exhibited at the DNP booth, situated at East Hall 6, E5936 at SEMICON Japan 2025, to be held December 17–19 at Tokyo Big Sight.

- 1 Nanoimprint Lithography (NIL): A microfabrication technology that presses a mold template onto a substrate, typically a resin, to reliably and inexpensively transfer circuit patterns with line widths from the nanometer (nm) level, where a nanometer equals 10-9 meters) to the micrometer (μm) level, where a micrometer equals 10-6 meters.

- 2 NILによる超微細半導体の省エネルギー加工技術 → https://www.dnp.co.jp/news/detail/10162455_1587.html

- Company and product names mentioned in this release are the trademarks or registered trademarks of their respective owners.

- Information contained in this release is current as of the date of announcement, and is subject to change without notice.