Se logró una resolución de patrones finos más allá de la generación de 2 nanómetros en fotomáscaras para litografía EUV

También comienza a ofrecer fotomáscaras para evaluar fotomáscaras EUV de alta NA para semiconductores de próxima generación.

12 de diciembre de 2024

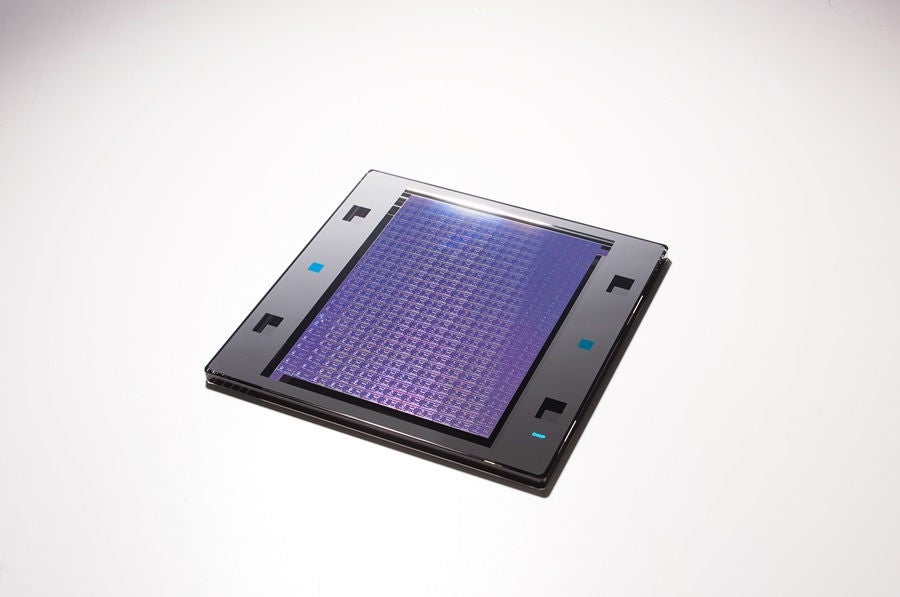

Dai Nippon Printing Co., Ltd. (DNP) ha logrado obtener la resolución de patrón fino requerida para fotomáscaras para semiconductores lógicos de la generación de 2 nanómetros (nm: 10-9 m) y superiores *1, compatibles con la litografía EUV (ultravioleta extremo), el proceso de vanguardia en la fabricación de semiconductores.

Además, DNP ha completado la evaluación básica de fotomáscaras compatibles con alta apertura numérica (alta NA) *2, que se están considerando para su uso en semiconductores de próxima generación a partir de la generación de 2 nm en adelante, y ha comenzado a proporcionar fotomáscaras de evaluación a consorcios de desarrollo de semiconductores, fabricantes de equipos de fabricación, fabricantes de materiales, etc. La litografía EUV de alta NA permite formar patrones finos con mayor resolución que los métodos convencionales en obleas de silicio y, por lo tanto, se espera que conduzca a la realización de semiconductores de alto rendimiento y bajo consumo de energía.

Fotomáscaras para litografía EUV a partir de la generación de 2 nanómetros

Fotomáscaras para litografía EUV a partir de la generación de 2 nanómetros

En los últimos años, la producción en masa de semiconductores lógicos de vanguardia mediante litografía EUV, que utiliza una fuente de luz EUV, ha progresado aún más, y su adopción también se está expandiendo en los semiconductores de memoria, lo que hace que la litografía EUV sea indispensable para el suministro de semiconductores de vanguardia.

En 2023, DNP completó el desarrollo *3 de un proceso de fabricación de fotomáscaras para litografía EUV de generación de 3 nm. En 2024, DNP participó como subcontratista en el "Proyecto de Investigación y Desarrollo para el Fortalecimiento de la Infraestructura del Sistema de Información y Comunicaciones Post-5G" de la Organización para el Desarrollo de Nuevas Energías y Tecnología Industrial (NEDO), en el que también participa Rapidus Inc. (sede central: Tokio; presidente y director ejecutivo: Koike Atsuyoshi), y está desarrollando *4 tecnologías relacionadas con los procesos de fabricación de fotomáscaras y garantías para semiconductores lógicos de vanguardia.

[Descripción general del desarrollo]

DNP ahora ha tenido éxito en resolver los patrones finos requeridos para fotomáscaras para semiconductores lógicos de la generación de 2 nm y más allá, en fotomáscaras para litografía EUV, con vistas a una fabricación de semiconductores de vanguardia. Además, DNP también ha completado la evaluación básica de fotomáscaras EUV compatibles con alta NA, que se están considerando para su uso en semiconductores de próxima generación de la generación de 2 nm y más allá, y ha comenzado a ofrecer máscaras de muestra.

[Puntos clave del desarrollo]

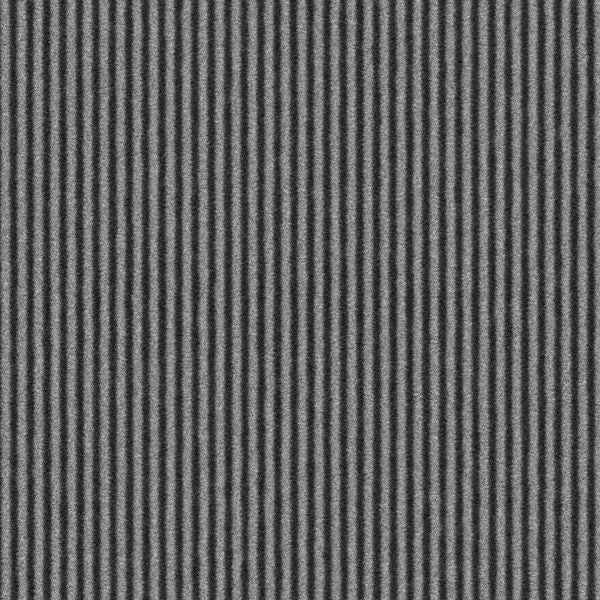

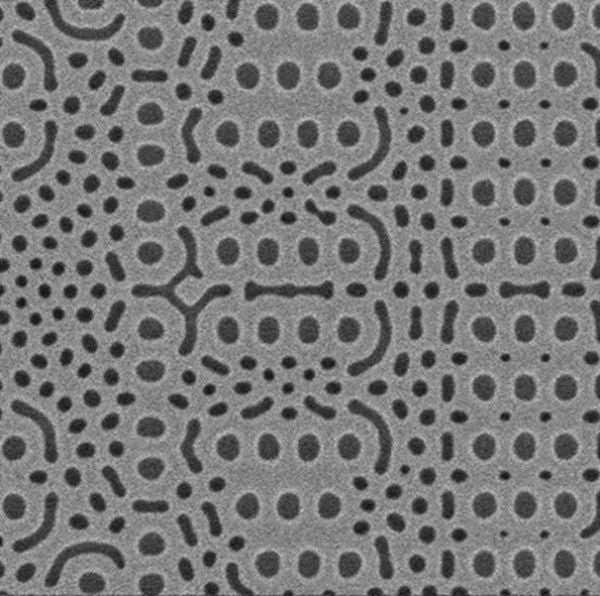

- Para crear fotomáscaras para litografía EUV en la generación de 2 nm y posteriores, se requieren patrones un 20 % más pequeños que los de la generación de 3 nm. Se requiere tecnología para resolver todos los patrones finos en la misma máscara, incluyendo no solo patrones rectos y rectangulares estándar, sino también patrones curvos cada vez más complejos. DNP ha logrado la resolución de patrón requerida para la generación de 2 nm y posteriores mediante mejoras constantes basadas en su proceso de fabricación establecido para la generación de 3 nm.

Imagen de patrón de línea y espacio con un ancho de línea de 17 nm en una fotomáscara para litografía EUV

Imagen de patrón de línea y espacio con un ancho de línea de 17 nm en una fotomáscara para litografía EUV

Imagen de patrón curvo fino en una fotomáscara para litografía EUV

Imagen de patrón curvo fino en una fotomáscara para litografía EUV

- Las fotomáscaras para litografía de alta NA-EUV requieren mayor precisión y un procesamiento más fino que las de litografía EUV convencional. DNP ha establecido y optimizado un flujo de proceso de fabricación diferente al utilizado para las fotomáscaras de litografía EUV convencionales.

[Desarrollos futuros]

DNP continuará desarrollando tecnologías de producción, incluyendo aquellas destinadas a mejorar el rendimiento de fabricación, con el objetivo de iniciar la producción en masa de fotomáscaras para semiconductores lógicos de 2 nm en el año fiscal 2027. Además, DNP seguirá cooperando con imec, un instituto de investigación internacional de vanguardia con sede en Bélgica, para promover el desarrollo de tecnologías de fabricación de fotomáscaras con miras a la generación de 1 nm. DNP promoverá el desarrollo en colaboración con diversos socios de la industria internacional de semiconductores y contribuirá al crecimiento de la industria japonesa de semiconductores.

*1 Cumple con los estándares de la Hoja de Ruta Internacional para Dispositivos y Sistemas (IRDS)

*2 La apertura numérica (NA) es un valor que indica el brillo y el poder de resolución de un sistema óptico. Una NA alta se refiere a la expansión de la apertura numérica del objetivo en equipos de exposición EUV, de los valores convencionales de 0,33 a 0,55.

*3 3ナノメートル相当のEUVリソグラフィ向けフォトマスク製造プロセスを開発(2023年12月12日)→ https://www.dnp.co.jp/news/detail/20170116_1587.html

*4 2ナノメートル世代のEUVリソグラフィ向けフォトマスク製造プロセス開発を加速(2024年3月27日) → https://www.dnp.co.jp/news/detail/20173719_1587.html

- Las especificaciones del producto y los detalles del servicio descritos están actualizados a la fecha de publicación y pueden estar sujetos a cambios sin previo aviso.