Desarrollo de una plantilla de nanoimpresión con un ancho de línea de circuito de 10 nm para semiconductores de última generación

Satisface la necesidad de anchos de línea de circuito más finos y costos de fabricación reducidos para semiconductores equivalentes a la generación de 1,4 nm

9 de diciembre de 2025

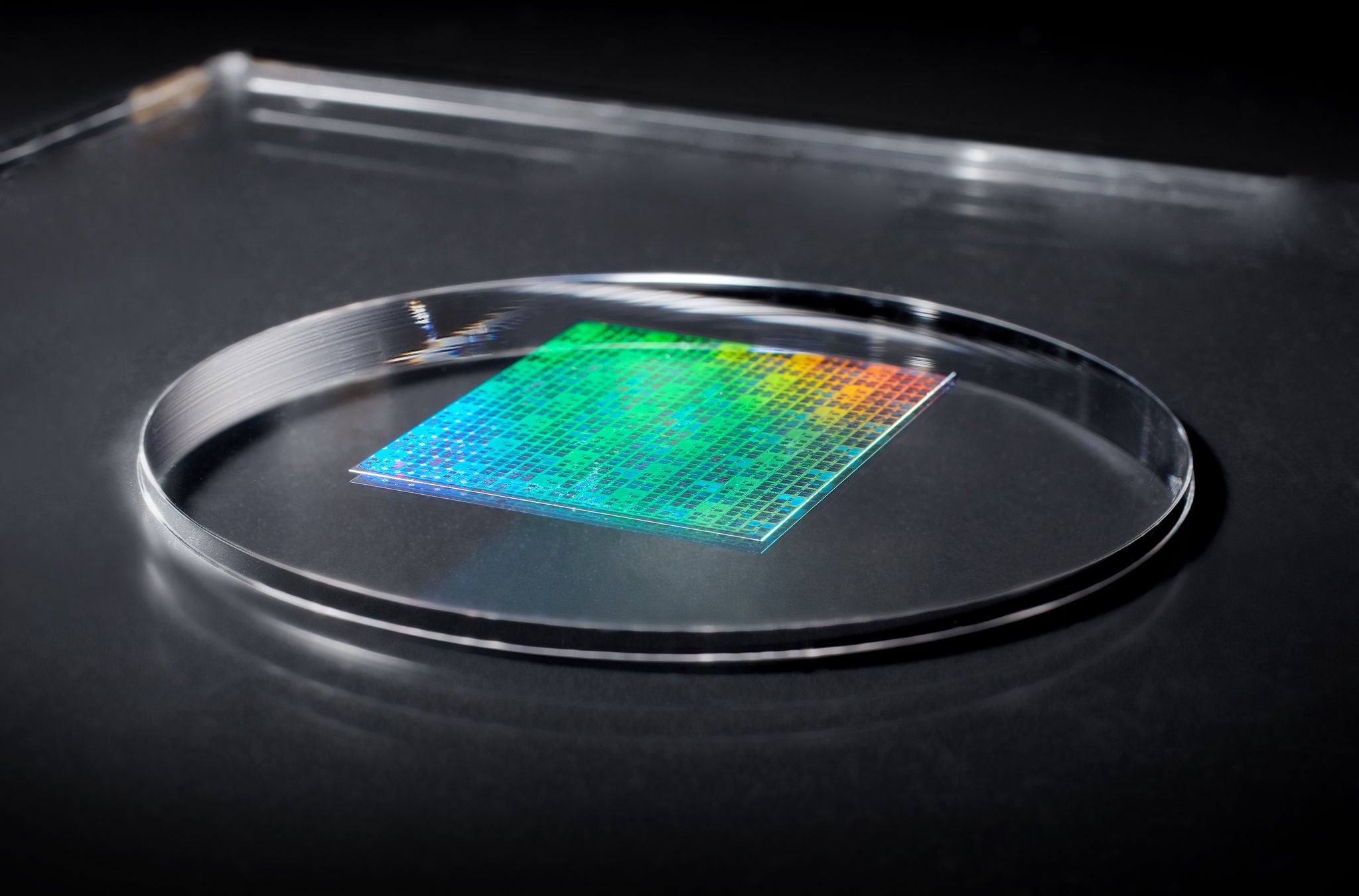

Dai Nippon Printing Co., Ltd. (sede: Tokio, presidente y director ejecutivo: Kitajima Yoshinari, en adelante, "DNP") ha desarrollado una plantilla (molde) con un ancho de línea de circuito de 10 nm para litografía de nanoimpresión (NIL)*1, utilizada para formar patrones de circuitos semiconductores. Esta plantilla también es compatible con semiconductores lógicos equivalentes a la generación de 1,4 nanómetros (1 nm = una milmillonésima parte de un metro). Esta nueva plantilla NIL, con un ancho de línea de 10 nm, satisfará las necesidades de miniaturización de los semiconductores lógicos de vanguardia utilizados en dispositivos como teléfonos inteligentes y centros de datos, además de la memoria flash NAND.

Objetivos e historia del desarrollo de plantillas NIL

En los últimos años, a medida que diversos dispositivos se han vuelto más sofisticados, se ha incrementado la demanda de una mayor miniaturización en semiconductores de vanguardia, y la producción mediante litografía EUV (ultravioleta extremo) está progresando. Sin embargo, dado que se requieren costos y energía relativamente altos para construir líneas de producción y el proceso de exposición, ha surgido una necesidad urgente de reducir los costos de fabricación y, al mismo tiempo, el impacto ambiental. Desde 2003, DNP ha estado desarrollando plantillas NIL que pueden reducir el consumo de energía en el proceso de exposición mediante la impresión y transferencia directa de una plantilla grabada con un patrón de circuito sobre un sustrato, y desde entonces ha acumulado una experiencia única.

DNP ha desarrollado una plantilla NIL de 10 nm que puede sustituir parte del proceso de litografía EUV y permitir la fabricación de semiconductores lógicos de vanguardia, satisfaciendo así las necesidades de los clientes que no cuentan con procesos de producción de litografía EUV. Con esta plantilla, DNP ampliará las opciones disponibles para sus procesos de fabricación de semiconductores, lo que se traducirá en una reducción de los costes de fabricación y un menor impacto ambiental.

Características de la plantilla NIL recientemente desarrollada con un ancho de línea de circuito de 10 nm

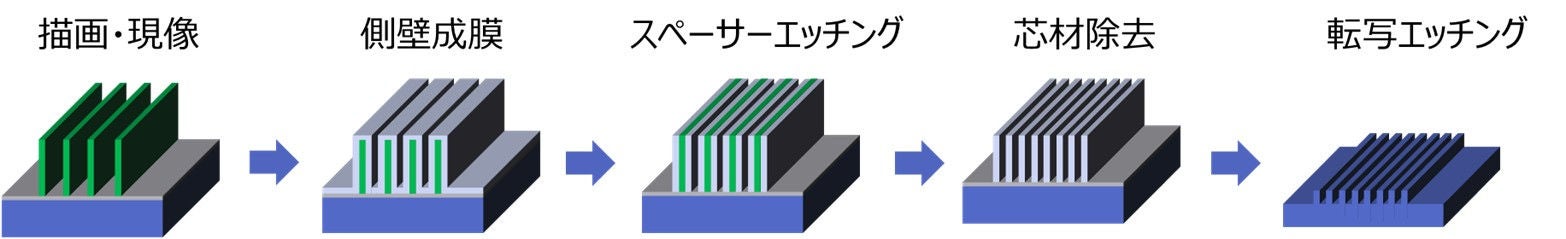

La miniaturización de las plantillas NIL se logró mediante el uso de patrones dobles autoalineados (SADP), que duplica la densidad del patrón al aplicar deposición de película y grabado al patrón formado por el sistema de litografía.

Además de la tecnología de fabricación de fotomáscaras y los conocimientos técnicos que DNP ha cultivado, la empresa también ha aplicado su tecnología de proceso de fabricación de obleas para desarrollar una plantilla NIL con un ancho de línea de circuito de 10 nm.

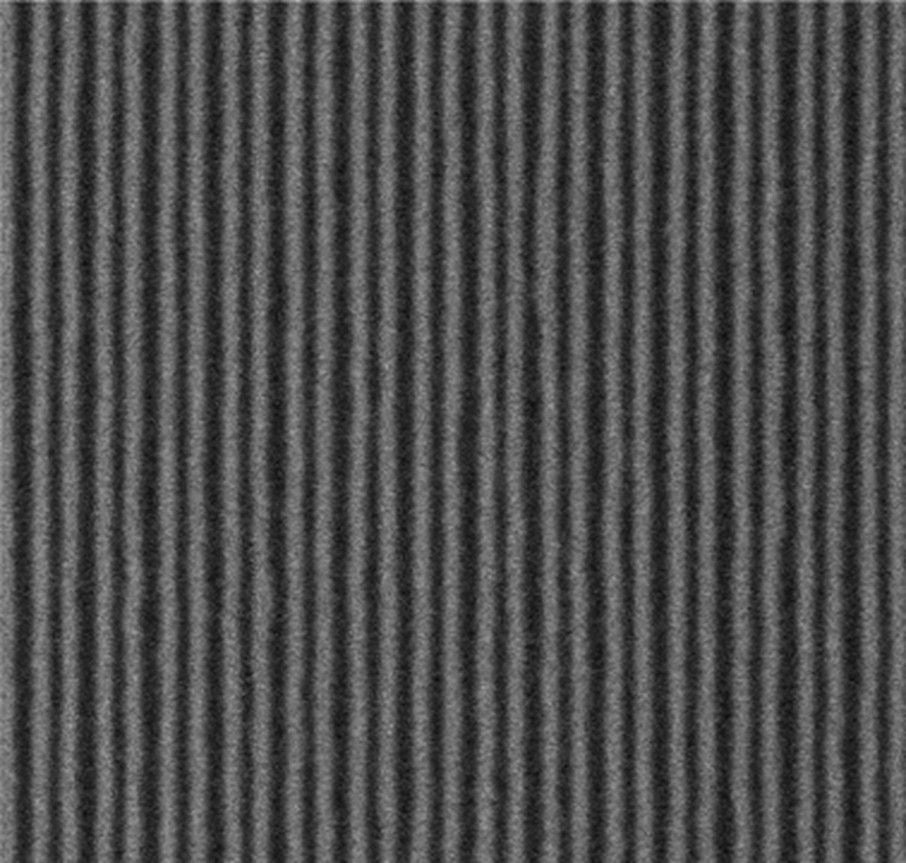

Imagen de patrón de línea y espacio con un ancho de línea de 10 nm en una fotomáscara de nanoimpresión

Imagen de patrón de línea y espacio con un ancho de línea de 10 nm en una fotomáscara de nanoimpresión

- Satisface la necesidad de anchos de línea de circuito más finos en semiconductores lógicos de vanguardia, que se espera que se expandan aún más en el futuro.

Reduce el consumo de energía en el proceso de exposición en la fabricación avanzada de semiconductores. La tecnología de procesamiento de ahorro de energía para semiconductores ultrafinos con NIL reduce el consumo de energía a aproximadamente una décima parte del de los procesos de exposición convencionales, como la inmersión en fluoruro de argón (ArF) y la radiación ultravioleta extrema (UVE). *2

Desarrollos futuros

DNP está profundizando el diálogo con fabricantes de semiconductores y otros clientes, anticipándose a las necesidades de miniaturización de semiconductores, y ha comenzado el trabajo de evaluación de plantillas NIL, con el objetivo de iniciar la producción en masa en 2027. De cara al futuro, con miras a una mayor miniaturización y reducción de costos en semiconductores, DNP continuará promoviendo un mayor desarrollo de plantillas NIL y fortaleciendo su sistema de producción para satisfacer la creciente demanda, con el objetivo de aumentar las ventas de NIL en 4 mil millones de yenes en el año fiscal 2030.

El producto se exhibirá en el stand de DNP (East Hall 6, Stand No. E5936) en SEMICON Japan 2025, que se llevará a cabo en Tokyo Big Sight (Centro Internacional de Exposiciones) del 17 al 19 de diciembre de 2025.

- 1 Litografía por nanoimpresión: una tecnología de microfabricación que implica presionar una plantilla de molde sobre un sustrato, como resina, para transferir de manera estable y económica patrones de circuitos con anchos de línea en el rango de nm (nanómetros: 10-9 metros) a μm (micrómetros: 10-6 metros).

- 2 NILによる超微細半導体の省エネルギー加工技術 → https://www.dnp.co.jp/news/detail/10162455_1587.html

- Los nombres de empresas y productos enumerados son marcas comerciales o marcas comerciales registradas de las respectivas empresas.

- La información proporcionada es actual a la fecha de publicación y puede estar sujeta a cambios sin previo aviso.