开发用于相当于3纳米的EUV光刻的光掩模制造工艺

满足电路线宽不断微细化的半导体市场需求

2023年12月12日

大日本印刷株式会社 (总公司:东京代表取缔役社长:北岛义齐以下简称:DNP) 开发出了相当于3纳米 (nm:10-9 m) 的光掩膜制造工艺,适用于半导体制造的尖端工艺EUV (ExtremeUltra-Violet:极紫外) 光刻。随着智能手机和数据中心等使用的逻辑半导体的高性能化,满足了线路宽度的微细化需求。

随着DNP获得SCIVAX股份的部分转让而成为SCIVAX的股东,两家公司将DNP的批量生产专业知识与SCIVAX的批量生产制造设备的优势相结合,以满足国内外制造商对纳米压印产品的批量生产需求。

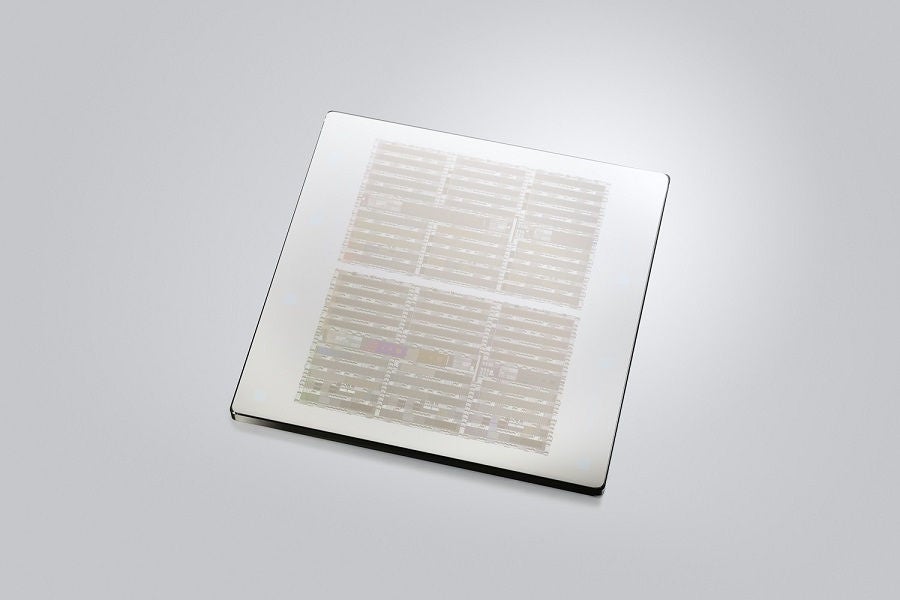

用于EUV光刻的光掩膜相当于3纳米

用于EUV光刻的光掩膜相当于3纳米

【开发背景】

近年来,使用EUV光源的EUV光刻技术已经确立,最先进的逻辑半导体正在通过EUV光刻进行生产。2023年将提供采用3nm逻辑半导体的产品,预计半导体电路宽度的小型化将继续发展。此外,EUV光刻在存储器半导体中的采用正在进行中,并且EUV对应对于供应最先进的半导体是必不可少的。

DNP于2016年作为光掩膜专业制造商在世界上首次导入了多电子束掩膜绘制装置*1,以高生产率和高品质满足了半导体制造商的要求。另外,2020年开发了相当于5nm工艺的EUV光刻用光掩膜制造工艺*2,开始供应满足半导体相关市场需求的掩膜。为了满足进一步小型化的需求,我们开发了相当于3纳米工艺的EUV光刻光掩模。

【开发概要】

○DNP于2016年推出的多电子束掩模绘图仪能够照射大约26万束电子束,即使对于复杂的图案形状,也可以大大缩短绘图时间。我们改进了制造工艺,充分利用了该设备的特性,优化了数据校正技术和加工条件,以适应EUV光刻光罩的复杂曲线图案结构。

○DNP将增加一台新的多电子束掩模绘图仪,并将于2024年下半年投入运营。强化EUV光刻用光掩膜等尖端领域半导体制造的应对。

○我们正在与总部设在比利时的最先进的国际研究机构imec (Interuniversity Microelectronics Centre) 合作开发用于下一代EUV曝光设备的光掩模。

【今后的发展】

DNP将向全球半导体厂商、半导体开发联盟、制造设备厂商、材料厂商等提供此次开发的相当于3nm的EUV光刻用光掩膜,同时还将支援EUV光刻的周边技术开发,力争到2030年实现年销售额100亿日元。通过与imec等合作伙伴的联合开发,DNP还将继续开发比3纳米更精细的2纳米工艺。

*1 2016年12月13日新闻发布:强化新一代半导体光掩膜生产体制

*2 2020年7月10日新闻发布:开发用于5nm兼容EUV光刻的光掩模工艺

- 在“SEMICON Japan 2023”上,我们将介绍用于EUV光刻的光掩膜。

- 所记载的公司名、商品名是各公司的商标或注册商标。

- 新闻稿中描述的产品规格,服务内容等截至发布日期。之后可能会发生变更,恕不另行通知,敬请谅解。