加速开发用于2纳米EUV光刻的光掩模制造工艺

作为Rapidus的再委托方参与NEDO的“后5G信息通信系统基础强化研究开发事业”

2024年3月27日

大日本印刷株式会社 (总公司:东京代表取缔役社长:北岛义齐以下简称:DNP) 正式开始开发用于2纳米 (nm:10-9 m) 逻辑半导体的光掩膜制造工艺,该工艺支持半导体制造最尖端工艺EUV (ExtremeUltra-Violet:极紫外) 光刻。

DNP此次作为再委托方参与了Rapidus株式会社 (总公司:东京代表取缔役社长:小池淳义) 参与的国立研究开发法人新能源产业技术综合开发机构 (NEDO) 的“后5G信息通信系统基础强化研究开发事业”,提供本制造工艺及保修相关技术。

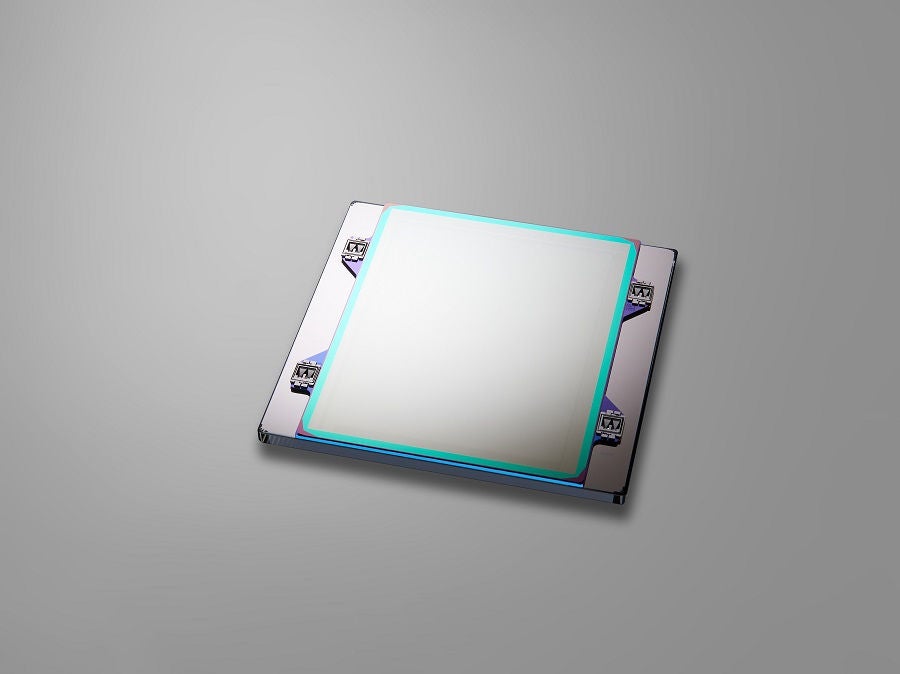

用于EUV光刻的光掩膜,带有光掩膜保护膜*1

用于EUV光刻的光掩膜,带有光掩膜保护膜*1

【发展背景和概要】

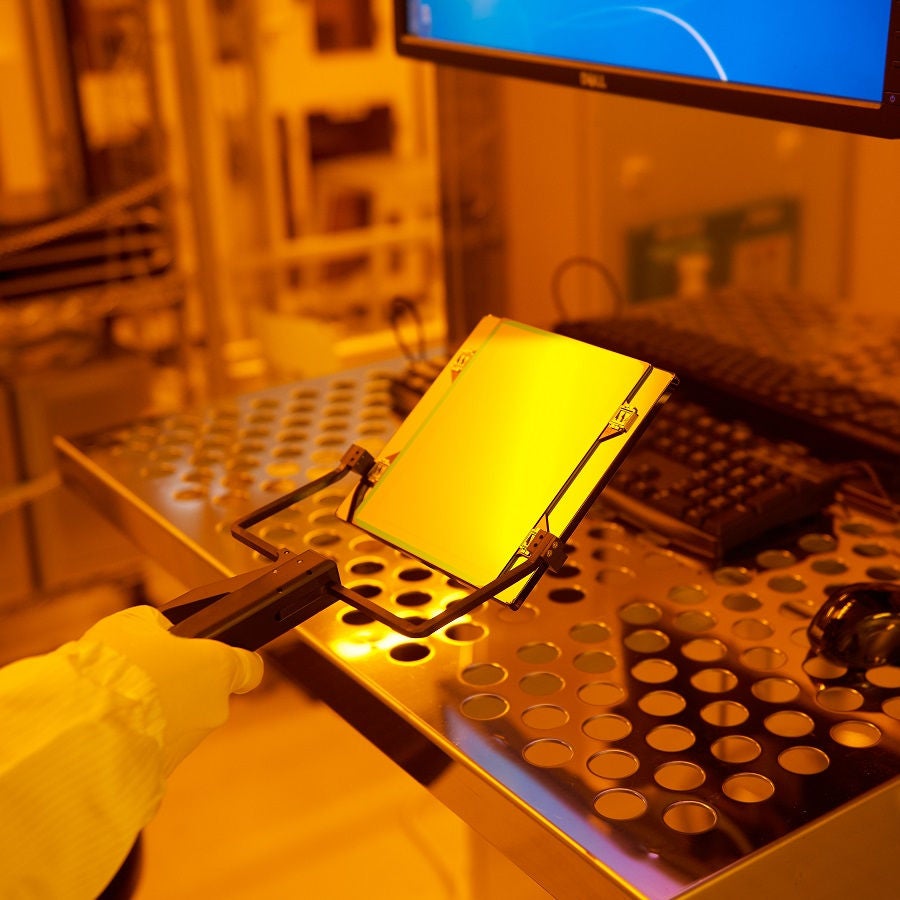

近年来,在最先进的逻辑半导体中,使用EUV光源的EUV光刻正在进行生产。DNP于2016年作为光掩膜专业制造商在世界上首次导入了多电子束掩膜绘制装置等*2,强化了具备高生产率和高品质的尖端领域半导体制造的对应。2023年,我们完成了用于EUV光刻的3纳米光掩模制造工艺的开发*3,并开始了2纳米工艺的开发。

为满足此次进一步微细化的需求,我们将在2024年度内启动第2台和第3台多电子束掩膜绘制装置等,正式开发面向2纳米EUV光刻的光掩膜制造工艺。

另外,DNP作为再委托方参与了在NEDO的“后5G信息通信系统基础强化研究开发事业”中由Rapidus株式会社受托进行的“ (d1) 高集成度最尖端逻辑半导体制造技术开发”项目。

【今后的发展】

DNP将在2025年度之前,完成支持EUV光刻的2纳米工艺逻辑半导体用光掩膜制造工艺的开发,2026年度以后,以2027年度开始量产为目标,推进生产技术的确立。

此外,我们还开始开发2纳米或更高世代,并与总部设在比利时的最先进的国际研究机构imec签署了一项协议,共同开发下一代EUV光掩模。

DNP通过与国际半导体产业的各种合作伙伴合作促进发展,为日本半导体产业的发展做出贡献。

*1在转印2纳米半导体电路时,EUV光刻光掩膜上的异物可能会降低半导体制造的成品率。DNP将推动光掩膜制造工艺的发展,该工艺适用于带保护膜的EUV。

*2 2023年12月12日ニュースリリース:3ナノメートル相当のEUVリソグラフィ向けフォトマスク製造プロセスを開発 → https://www.dnp.co.jp/news/detail/20170116_1587.html

*3 2016年12月13日ニュースリリース:次世代半導体用フォトマスクの生産体制を強化 → https://www.dnp.co.jp/news/detail/1187660_1587.html

- 所记载的公司名、商品名是各公司的商标或注册商标。

- 所列产品规格、服务内容等均为发布日期。之后可能会发生变更,恕不另行通知,敬请谅解。