Entwicklung einer Nanoimprint-Vorlage mit einer Leiterbahnbreite von 10 nm für hochmoderne Halbleiter

Erfüllt den Bedarf an feineren Leiterbahnbreiten und reduzierten Herstellungskosten für Halbleiter, die der 1,4-nm-Generation entsprechen.

9. Dezember 2025

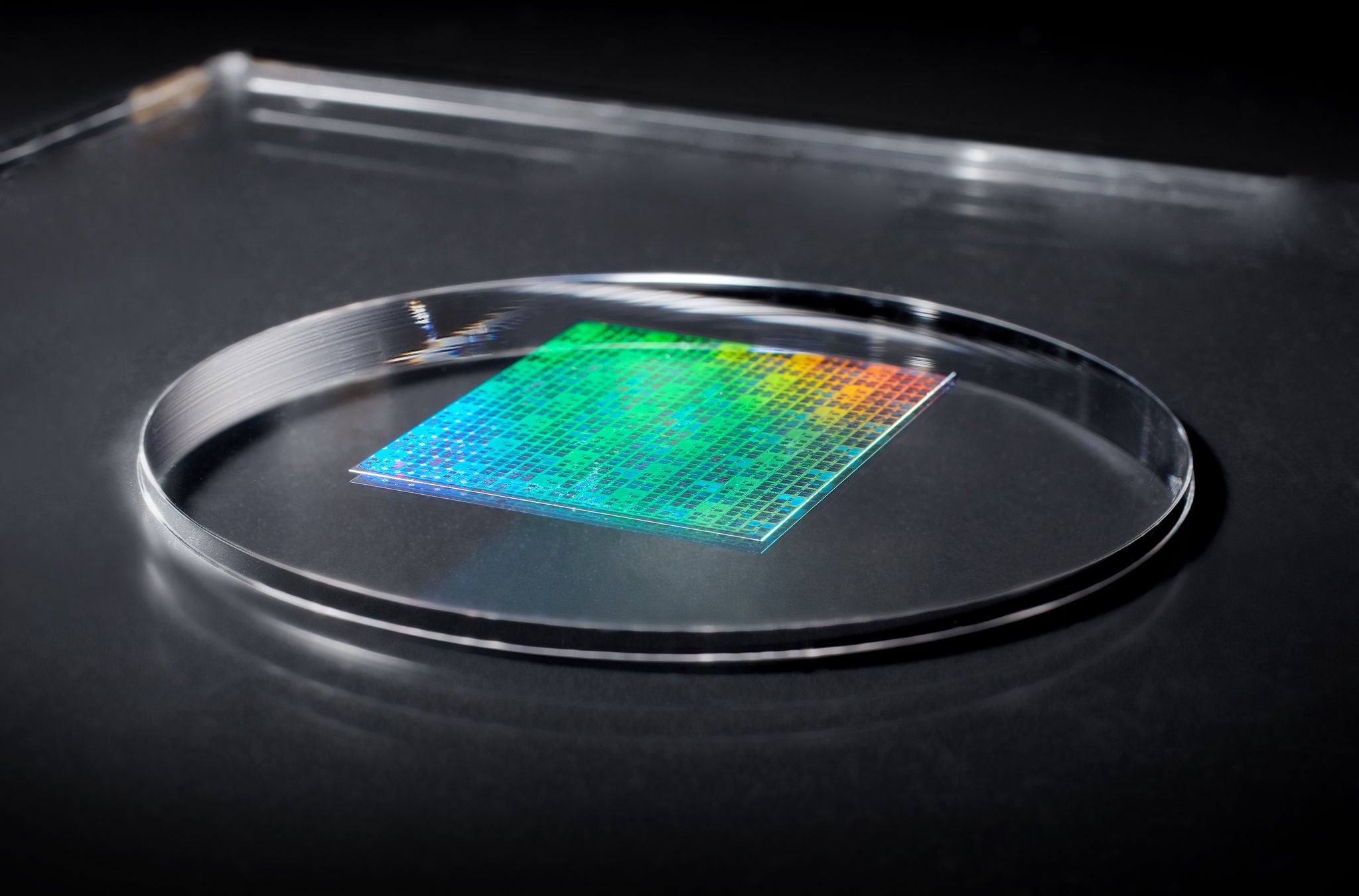

Dai Nippon Printing Co., Ltd. (Hauptsitz: Tokio, Präsident und CEO: Kitajima Yoshinari, im Folgenden „DNP“ genannt) hat eine Schablone (Form) mit einer Leiterbahnbreite von 10 nm für die Nanoimprint-Lithographie (NIL)*1 entwickelt. Diese dient zur Herstellung von Halbleiterschaltungen und ist mit Logikhalbleitern der 1,4-Nanometer-Generation (1 nm = 1 Milliardstel Meter) kompatibel. Die neu entwickelte NIL-Schablone mit einer Leiterbahnbreite von 10 nm erfüllt die Miniaturisierungsanforderungen modernster Logikhalbleiter, die in Geräten wie Smartphones und Rechenzentren sowie in NAND-Flash-Speichern eingesetzt werden.

Ziele und Geschichte der Entwicklung von NIL-Vorlagen

In den letzten Jahren ist mit der zunehmenden Komplexität verschiedenster Geräte der Bedarf an noch größerer Miniaturisierung in der Halbleitertechnik gestiegen, und die Produktion mittels EUV-Lithografie (Extreme Ultraviolett) schreitet voran. Da jedoch der Aufbau von Produktionslinien und der Belichtungsprozess relativ hohe Kosten und einen hohen Energieverbrauch verursachen, besteht ein dringender Bedarf, die Herstellungskosten zu senken und gleichzeitig die Umweltbelastung zu reduzieren. Seit 2003 entwickelt DNP NIL-Templates, die den Energieverbrauch im Belichtungsprozess durch direktes Pressen und Übertragen eines mit einem Schaltungsmuster gravierten Templates auf ein Substrat reduzieren und hat sich seitdem einzigartiges Know-how angeeignet.

DNP hat eine 10-nm-NIL-Vorlage entwickelt, die Teile des EUV-Lithographieprozesses ersetzen und die Herstellung hochmoderner Logikhalbleiter ermöglichen kann. Damit werden die Bedürfnisse von Kunden erfüllt, die keine EUV-Lithographie-Produktionsprozesse betreiben. Durch die Bereitstellung dieser Vorlage erweitert DNP die Optionen für die Halbleiterfertigung seiner Kunden und trägt so zu geringeren Fertigungskosten und einer reduzierten Umweltbelastung bei.

Merkmale der neu entwickelten NIL-Vorlage mit einer Leiterbahnbreite von 10 nm

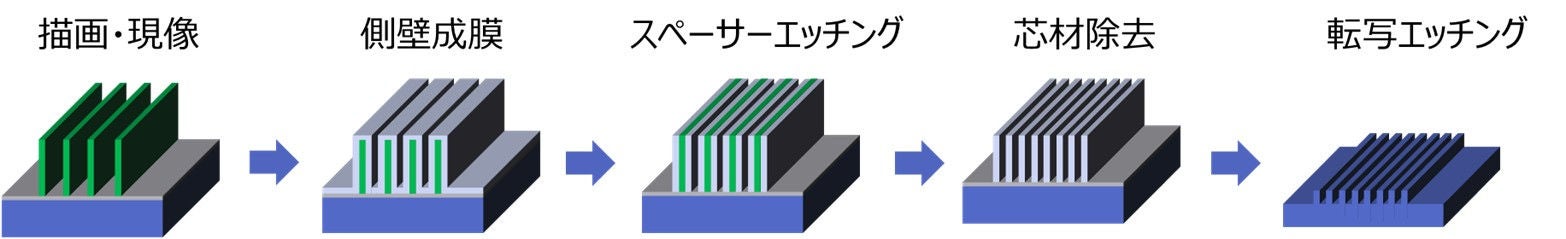

Die Miniaturisierung von NIL-Vorlagen wurde durch die Verwendung von selbstjustierender Doppelstrukturierung (SADP) erreicht, die die Musterdichte verdoppelt, indem Filmbeschichtung und Ätzung auf das durch das Lithographiesystem erzeugte Muster angewendet werden.

Zusätzlich zu der von DNP entwickelten Technologie und dem Know-how zur Herstellung von Fotomasken hat das Unternehmen auch seine Technologie zur Herstellung von Wafern eingesetzt, um eine NIL-Vorlage mit einer Leiterbahnbreite von 10 nm zu entwickeln.

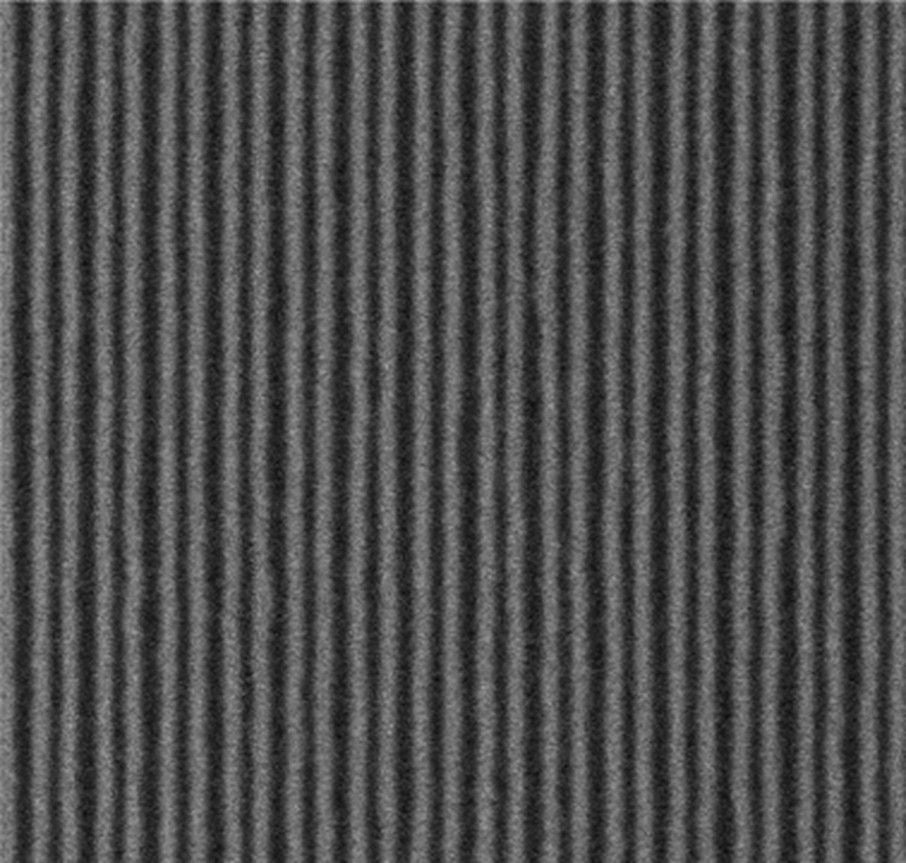

Linien- und Zwischenraummusterbild mit einer Linienbreite von 10 nm auf einer Nanoimprint-Fotomaske

Linien- und Zwischenraummusterbild mit einer Linienbreite von 10 nm auf einer Nanoimprint-Fotomaske

- Erfüllt den Bedarf an feineren Leiterbahnbreiten in modernen Logik-Halbleitern, deren Verbreitung in Zukunft voraussichtlich noch weiter zunehmen wird.

Reduziert den Energieverbrauch bei der Belichtung in der modernen Halbleiterfertigung. „Energiesparende Verarbeitungstechnologie für ultrafeine Halbleiter mittels Nanoimprint-Lithographie“ reduziert den Energieverbrauch auf etwa ein Zehntel des Energieverbrauchs herkömmlicher Belichtungsverfahren wie ArF-Immersion (Argonfluorid) und EUV. *2

Zukünftige Entwicklungen

DNP intensiviert den Dialog mit Halbleiterherstellern und anderen Kunden, um den Bedarf an Halbleiterminiaturisierung frühzeitig zu erkennen, und hat mit der Evaluierung von NIL-Templates begonnen. Ziel ist es, die Massenproduktion im Jahr 2027 aufzunehmen. Mit Blick auf die weitere Miniaturisierung und Kostensenkung bei Halbleitern wird DNP die Weiterentwicklung von NIL-Templates vorantreiben und sein Produktionssystem stärken, um der steigenden Nachfrage gerecht zu werden. Ziel ist es, den NIL-Umsatz im Geschäftsjahr 2030 um 4 Milliarden Yen zu steigern.

Das Produkt wird auf dem DNP-Stand (Osthalle 6, Standnummer E5936) auf der SEMICON Japan 2025 ausgestellt, die vom 17. bis 19. Dezember 2025 im Tokyo Big Sight (Internationales Ausstellungszentrum) stattfindet.

- 1 Nanoimprint-Lithographie: Eine Mikrofertigungstechnologie, bei der eine Formvorlage auf ein Substrat wie beispielsweise Harz gepresst wird, um Schaltungsmuster mit Linienbreiten im Mikrofabrikationstechnik von nm (Nanometer: 10-9 Meter) bis μm (Mikrometer: 10-6 Meter) stabil und kostengünstig zu übertragen.

- 2 NILによる超微細半導体の省エネルギー加工技術 → https://www.dnp.co.jp/news/detail/10162455_1587.html

- Die aufgeführten Firmen- und Produktnamen sind Marken oder eingetragene Marken der jeweiligen Unternehmen.

- Die bereitgestellten Informationen sind zum Zeitpunkt der Veröffentlichung aktuell und können sich ohne vorherige Ankündigung ändern.