面向尖端半導體開發電路線寬10nm的納米壓印模板

支持相當於1.4nm工藝的半導體滿足電路線寬微細化和制造成本削減的需求

2025年12月9日

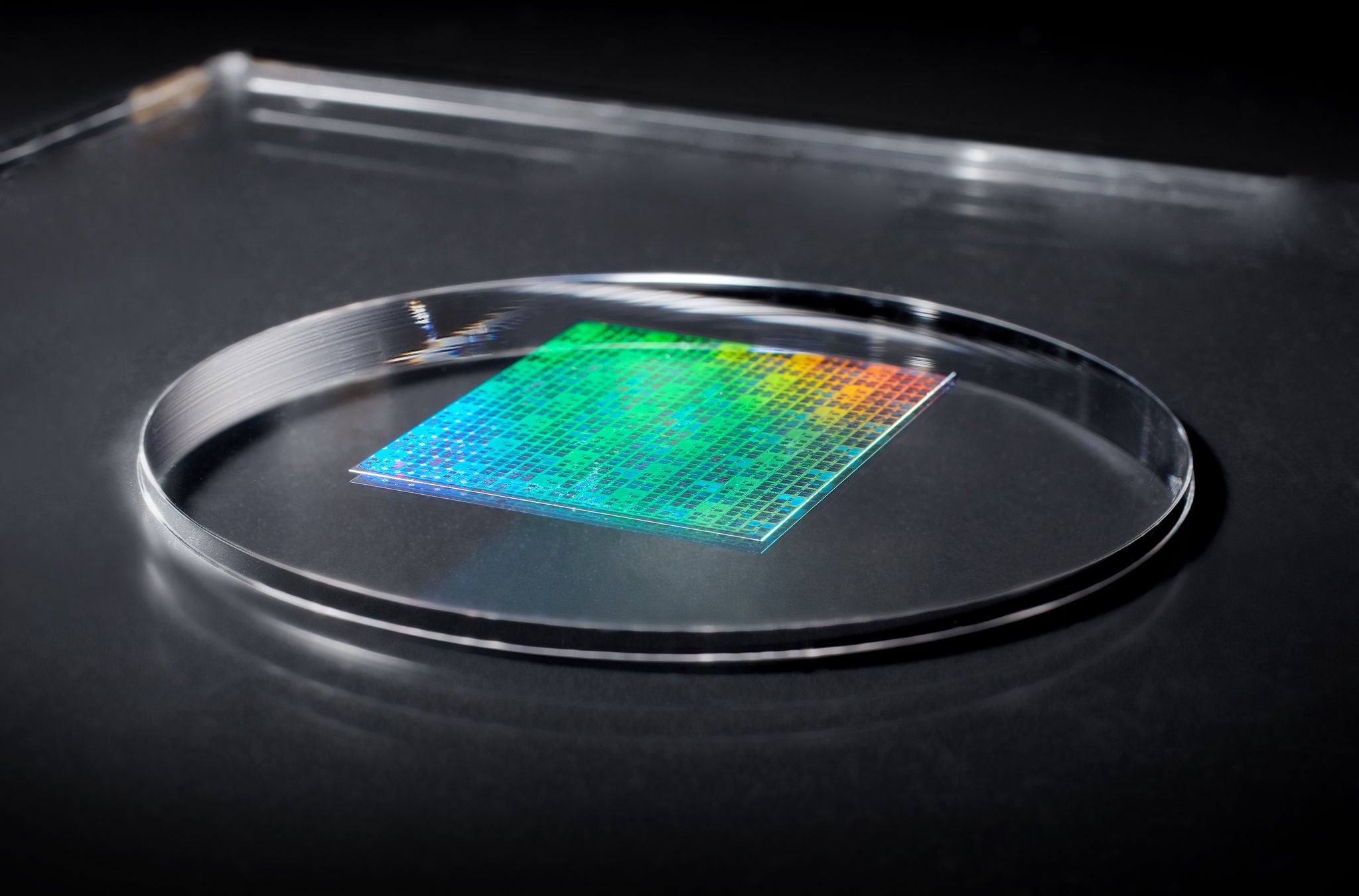

大日本印刷株式會社 (總公司:東京代表取締役社長:北島義齊以下簡稱:DNP) 面向用於形成半導體電路圖案的納米壓印光刻 (Nano-ImprintLithography:NIL) *1,開發出了線路寬度為10nm的模板 (型),可支持相當於1.4 nm (1nm=10億分之1米) 工藝的邏輯半導體。除了NAND型閃存之外,這次開發的線寬為10nm的NIL模板還滿足了智能手機和數據中心中使用的最先進邏輯半導體的小型化需求。

NIL模板開發的目標和背景

近年來,隨著各種設備的高性能,對尖端半導體的進一步微細化提出了要求,並且正在進行基於EUV (ExtremeUltra-Violet:極紫外線) 光刻的生產。同時,由於生產線的建設和曝光過程需要相對較高的成本和電力,因此迫切需要降低制造成本並減少對環境的影響。自2003年以來,DNP通過開發NIL模板積累了自己的專有技術,該模板可以通過將刻有電路圖案的模板直接壓印到電路板上來抑制曝光過程的功耗。

這次我們開發了線路寬度為10nm的NIL模板,可以制造尖端區域邏輯半導體,以滿足沒有EUV光刻生產工藝的EUV光刻替代部分步驟或客戶的需求。通過提供此模板,DNP將擴大客戶半導體制造工藝的選擇範圍,從而降低制造成本並減少對環境的影響。

新開發的線路寬度為10nm的NIL模板的特點

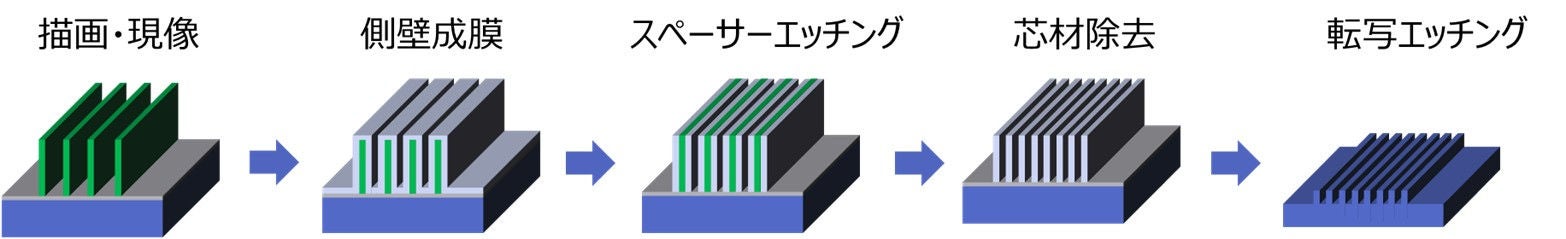

○利用雙圖案 (Self-AlignedDouble Patterning:SADP) 技術實現NIL模板的微細化,該技術通過對由繪圖裝置形成的圖案進行成膜和蝕刻,將圖案密度提高一倍。

○除了DNP培養的光掩膜制造技術和專業知識外,我們還應用晶圓制造工藝技術開發了線路寬度為10nm的NIL模板。

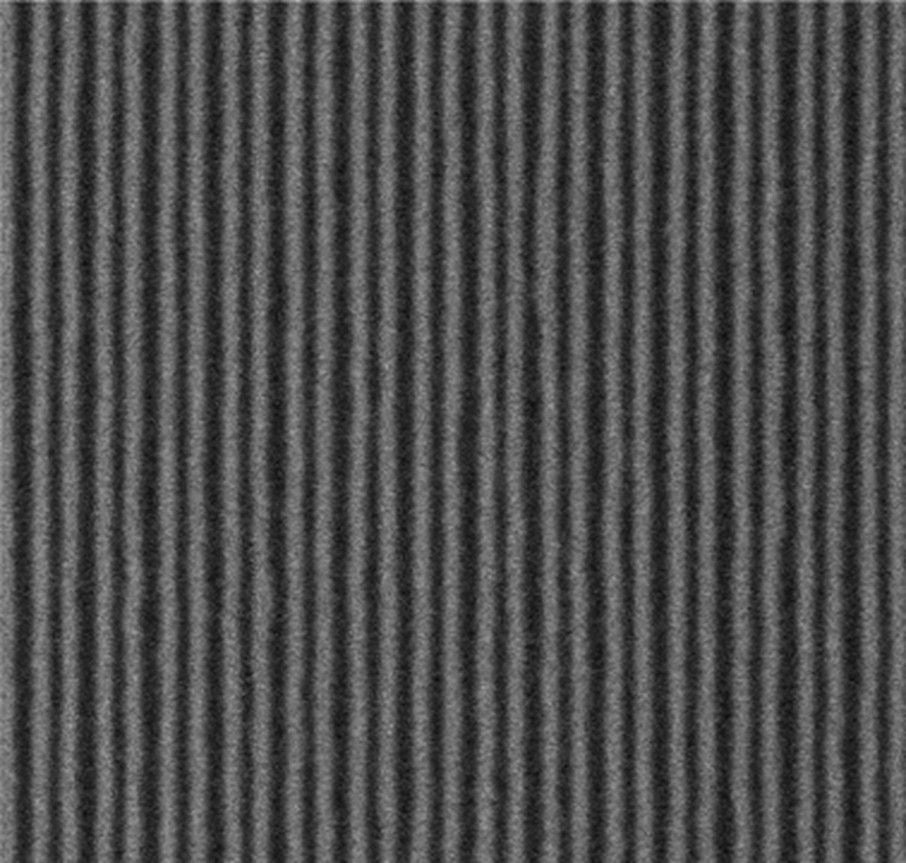

在奈米壓印光掩模上,線寬為10奈米的線-空圖案影像

在奈米壓印光掩模上,線寬為10奈米的線-空圖案影像

○可滿足今後有望進一步擴大的尖端邏輯半導體電路線寬的微細化需求。

○降低尖端半導體制造曝光工序的耗電量。通過“基於NIL的超細半導體節能加工技術”,與傳統的ArF (氟化氬) 浸漬和EUV等曝光工藝相比,功耗可降低至約1/10。※2

未來發展

DNP加深了與半導體制造商等客戶的對話,預測了半導體小型化的需求,開始了NIL模板的評估工作,並計劃在2027年開始批量生產。我們將繼續進一步開發NIL模板並加強生產係統,以滿足需求的擴大,進一步提高半導體的小型化和降低成本,我們的目標是在2030財年將NIL的銷售額增加40億日元。

該產品將於2025年12月17日至19日在東京國際展覽中心 (國際展覽中心) 舉行的“SEMICON Japan 2025”的DNP展位 (東6廳,展位編號:E5936) 展出。

- 1 奈米壓印光刻:一種微加工技術,它將模具模板壓到樹脂等基材上,以穩定且廉價的方式轉移線寬在奈米(nm:10-9 公尺)到微米(μm:10-6 公尺)微細加工技術電路圖案。

- 2 NILによる超微細半導体の省エネルギー加工技術 → https://www.dnp.co.jp/news/detail/10162455_1587.html

- 所記載的公司名、商品名是各公司的商標或註冊商標。

- 記載內容是發表日現在的內容。今後如有變更,恕不另行通知,敬請諒解。